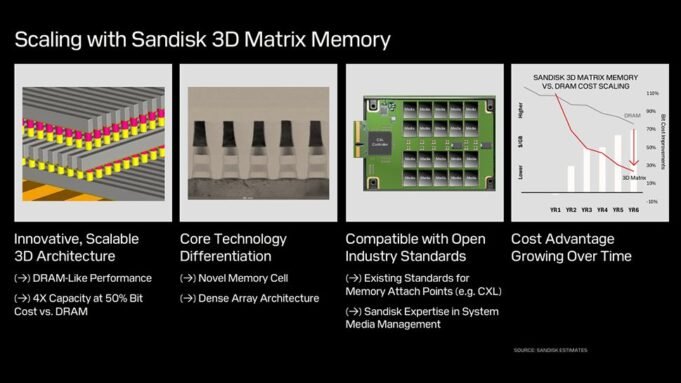

- Sandisk mengatakan bahwa memori matriks 3D akan menjadi pengganti yang terjangkau untuk DRAM

- Akan memberikan hasil tipe DRAM 4 kali kapasitas dan setengah dari biaya

- Sandisk mengatakan itu akan menjadi lebih terjangkau saat teknologi matang

Dalam sesi Hari Investor Sandisk 2.0 baru -baru ini, raksasa penyimpanan flash merilis serangkaian SSD baru, yang mencakup model pusat data 128TB, sambil menggambarkan peta jalannya yang ambisius untuk unit yang masih lebih besar: SSD 256 TB pada tahun 2026, SSD 512TB di 2027, dan kampanye besar 1 persen diperkirakan beberapa tahun kemudian.

Sandisk ingin sekali menenangkan investor yang mengejutkan setelahnya Digital Western DivideDan di luar membahas strateginya untuk meningkatkan pengembalian dan margin, perusahaan juga menghapus bungkus memori matriks 3D yang inovatif, sebuah teknologi memori yang dapat diskalakan yang, menurut laporan, menjanjikan kinerja yang mirip dengan DRAM empat kali berkapasitas dan setengah dari biaya dan setengah dari biaya dan setengahnya .

Sandisk telah memposisikan memori matriks 3D sebagai solusi yang terjangkau sebagai respons pada akhir hukum Moore untuk DRAM, di mana skala stagnasi, kesenjangan memori komputasi yang luas dan biaya memori yang tinggi telah menjadi tantangan penting. Perusahaan mengatakan bahwa arsitektur memori yang dapat diskalakan akan merusak “dinding memori”, memecahkan masalah kapasitas memori dan bandwidth yang berjuang untuk mempertahankan ritme dari meningkatnya tuntutan pemrosesan.

Lebih menguntungkan

Dikembangkan bekerja sama dengan IMEC, memori matriks 3D Sandisk didasarkan pada arsitektur matriks padat dengan desain sel memori baru sambil mempertahankan kompatibilitas dengan standar industri terbuka, seperti CXL.

Perusahaan menyatakan bahwa teknologi memori barunya akan semakin menguntungkan dari waktu ke waktu. Menurut grafik Sandisk bersama, pada tahun 6, memori matriks 3D akan mencapai lebih dari 50% penghematan biaya per bit dibandingkan dengan DRAM, dengan penurunan $/GB yang secara signifikan lebih jelas, yang menjadikannya alternatif yang lebih terjangkau untuk tradisional Solusi DRAM.

Peta pengembangan perusahaan, yang ditunjukkan di bawah ini, menjelaskan serangkaian tonggak sejarah, dengan transisi dari 150 mm WD FAB ke instalasi IMEC 300 mm pada tahun 2024, menandai langkah signifikan pertama dari teknologi menuju produksi skala besar.

Pada 2017, proyek ini telah berevolusi dari perangkat yang terisolasi ke matriks pasif, kendaraan pengembangan CMOS. Sampel Media Gen1 akan menjadi langkah besar berikutnya dan mereka diharapkan untuk mencapai kemampuan 32-64 Gbit, meskipun masih belum ada detail tentang kinerja kotor.